Funkamateur 10/88 |

Nach den ersten Veranstaltungen des Berliner "AC1"-Amateurcomputerclubs veröffentlichen wir auf dieser Seite, wie angekündigt, einige Vorschläge zur Verbesserung der Arbeit mit dem "AC1", die von Mitgliedern des Klubs erarbeitet wurden.

Im Interesse einer möglichst großen Nachbausicherheit haben

wir seinerzeit auch den Bildschirmteil

des "AC1" recht einfach gestaltet. Durch die absolute Priorität

der CPU kommt es bei Bildspeicherzugriffen,

besonders, wenn diese schnell hintereinander auftreten, zu

Störungen. Das kann insbesondere bei anspruchsvollen,

bewegten Grafikausgaben den Gesamteindruck erheblich

beeinträchtigen.

Die hier beschriebene kleine

Erweiterung beseitigt diesen Nachteil, gleich, ob mit schwarzem

oder weißem Hintergrund gearbeitet wird, erfordert aber eine

Zugriffszeit der BWS-RAM von weniger als 200 ns

(z.B. U 214 D 20, U 202 DA, 6516-15).

Außerdem ist, wie immer, sorgfältig zu arbeiten, da sonst

die Arbeit der CPU durch falsche oder gar

dauerhafte WAIT-Anforderungen blockiert wird und sozusagen gar nichts

mehr geht. Verschwinden die

Bildstörungen nicht, richtiger Aufbau vorausgesetzt, so ist die

Zugriffszeit der BWS-RAM doch größer

als 200 ns (bei getypten Bauelementen aber kaum zu befürchten).

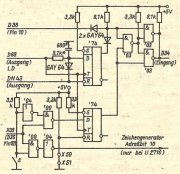

Vor der eigentlichen Umbauanleitung noch einige Worte zum

Funktionsprinzip. Auch bei einem CPU-Zugriff

erhält der Zeichengenerator den richtigen Kode, da in den zur

Verfügung stehenden 750 ns für ein Zeichen

sowohl die CPU als auch die Bildschirmsteuerung zugreifen können.

Dazu sind die ersten 500 ns für den

Schreib- oder Lesezyklus der CPU reserviert, in den restlichen 250 ns

versorgt sich die Bildschirmsteuerung

mit dem entsprechenden Zeichenkode. Damit die CPU auch sicher in das

für sie reservierte Zeitfenster kommt,

muß nötigenfalls mit WAIT etwas nachgeholfen werden.

Vergleiche mit einem "AC1" ohne diese WAIT-Logik zeigten

jedoch, daß praktisch keine merkliche Verzögerung entsteht,

auch nicht, wenn z.B. nur Bildschirmrollen erfolgt.

Die für diese Änderung erforderlichen zwei bzw. drei TTL-IS

sind z.B. auf dem Lochfeld der Grundleiterplatte

unterzubringen. Die eigentliche Umrüstung erfolgt in drei

Schritten:

1. Leitung am Ausgang von DG8 abtrennen und den oberen Teil der

Zusatzschaltung einfügen.

Die gestrichelt gezeichnete WAIT-Anforderung spart zwar ein Gatter,

läßt aber keine weitere WAIT-Quelle zu!

2. Einfügen des unteren Schaltungsteils zwischen dem Ausgang von

DG20 und den /WR-Eingängen der BWS-RAMs.

3. Leiterzug an Pin 11 von D45 (Dunkeltastung bei CPU-Zugriff)

abtrennen und diesen Pin auf H-Pegel legen

(3,3 kΩ an +5 V).

Das war's! Wer lieber schwarze Schrift auf weißem Grund

möchte, der fügt dann z.B. einen der verbliebenen

Negatoren (am besten schaltbar) in die Leitung zwischen D38, Pin 10 und

D34, Pin 12 ein.

Die beschriebene Bildschirmentstörung wurde inzwischen mehrfach

nachgebaut und funktioniert bei o.g.

Voraussetzungen problemlos.

|

| 76 KByte |

| kleine Erweiterung |

Als Hauptursache der Störimpulse auf dem Bildschirm beim Zugriff auf den Bildspeicher sehe ich das Fehlen einer definierten Bildinformation nach der Freigabe der Dunkeltastung an. Praktisch wird die Dunkeltastung schon aufgehoben, bevor durch den nächsten Zähler der Bildschirmsteuerung die Übertragung des nächsten Zeichens in das Schieberegister D38/39 angewiesen ist. Die Idee meiner Schaltung besteht nun darin, das Pixelsignal solange weiter dunkelzutasten, bis das Schieberegister neu geladen wird. Das Signal zum Laden liefert DG9. Die L/H-Flanke dieses Signals zeigt den Abschluß des Ladevorganges an. Ein L-Signal am Ausgang von DN43 zeigt einen Zugriff auf den BWS an. Dieses setzt nun ein D-FF zurück. Eine einfache Diodenkombination (oder auch ein DL 008-Gatter) verknüpft den Ausgang des D-FF mit dem Ausgang des Schieberegisters. Das D-FF wird mit der L/H-Flanke des LD-Signals (Ausgang DG9) beim nächsten Laden des Schieberegisters wieder gesetzt. Damit erreicht man, daß erst zu diesem Zeitpunkt keine Dunkeltastung des Videosignals mehr erfolgt. Die RC-Kombination (Werte evtl. experimentell ermitteln) am Dateneingang des D-FF sorgt dafür, daß das gleichzeitige Auftreten von L/H-Flanken an DG9 und DN43 (Ursache ist offensichtlich der gemeinsame Takt für Rechner und BS-Steuerung) ignoriert wird. Diese Schaltung habe ich mit einer Zeicheninvertierung ergänzt. Zur Speicherung der Invertierungsinformation benutzte ich das noch vorhandene zweite D-FF des D 174. Dieses wird wiederum von der H/L-Flanke des LD-Signals geladen. Die zu ladende Information entnimmt man an X 39. Eine EXOR-Gatteranordnung verknüpft das so gespeicherte Signal mit dem evtl. gerade dunkelgetasteten Pixelsignal. Über die (auch als Schalter ausführbaren) Steckkontakte X 50 und X 51 ist der gesamte Bildschirm invertierbar. Schalter S schaltet die Invertierung zu und den Grafiksatz des ZG ab.

|

| 61 KByte |

| Schaltung |