Funkamateur 12/88 |

Wer größere Schaltungen mit digitalen Schaltkreisen aufbaut,

diese eventuell aus älteren, nicht mehr benötigten

Schaltungen auslötet, möchte sie meist vorher auf ihre

richtige Funktion prüfen, um defekte IS sofort auszusondern,

und nicht später in mühseliger, manchmal stundenlanger

Prüfarbeit in der gesamten Schaltung zu suchen. Dies erfordert

aber für fast jeden IS-Typ eine entsprechende Prüfschaltung,

was letztlich sehr kostenaufwendig ist. Außerdem

verlangt der Prüfvorgang Zeit und setzt vom Prüfer die

Kenntnis der logischen Funktion der zu prüfenden IS voraus.

Die Unsitte falsch gepolte, falsch beschaltete oder kurzgeschlossene IS

durch Prüfen der Erwärmung mit dem Finger zu lokalisieren,

führt zwar oft schnell zum Erfolg, hat aber den Nachteil,

daß die Aufschriften verwischen.

Nachfolgend werden für den "AC1" eine Zusatzplatine und ein

Programm vorgestellt, mit denen es möglich ist,

die gebräuchlichsten Logik-IS der TTL- und LS-TTL-Reihe

sekundenschnell auf ihre richtige Funktion (statisch) zu

prüfen.

Bei der Entwicklung des Programms bin ich davon ausgegangen, daß

es nicht mehr als 896 Byte belegt und damit

auch in der kleinsten Ausbaustufe des "AC1" (nur 1 KByte

Arbeitsspeicher) lauffähig ist.

Zur Ein- und Ausgabe von Daten zwischen Computern

und seiner Umwelt werden normalerweise PIOs verwendet. Die

im Handel erhältlichen "UD 855 D S1" sind erst bei einer

Taktfrequenz unter 500 kHz einsetzbar und schieden damit

für den Einsatz in meiner Schaltung aus.

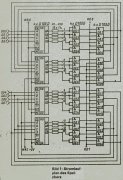

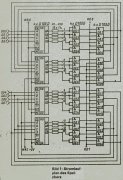

Eine andere Möglichkeit bietet das direkte Speicheraus- und

-einlesen. Bild 1 zeigt den

Stromlaufplan eines

2-Byte-Speichers. Dl bis D4 sind die eigentlichen Speicher. Jede IS

speichert 4 Bit. Die Eingänge dieser IS

liegen direkt am Datenbus. Die Ausgänge liegen mit der

Gatterkombination D5 bis D12 über Open-Kollektor-Stufen

am Datenbus. Die dazu erforderlichen Pull-up-Widerstände zwischen

Datenbus und +5 V sind auf der Grundleiterplatte

des "AC1" schon vorhanden.

Eingelesen werden die Daten, wenn an WR0 bzw. WR1 ein H-Impuls anlag.

Dabei werden sie mit der L/H-Flanke dieses

Impulses übernommen und erscheinen mit der H/L-Flanke an den

Ausgängen der D 195 D. Wenn RD0 bzw. RD1 H-aktiv

sind, werden die Daten aus dem Speicher ausgelesen.

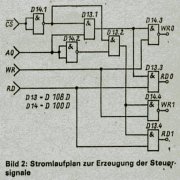

Bild 2 zeigt den Stromlaufplan

zur Erzeugung der Steuersignale. Um den Systemsteckverbinder für

die Speichererweiterung

freizuhalten, wurde ein zweiter Steckverbinder angebracht. Er

benötigt nur 14 Kontakte. Die Belegung dieses

Steckverbinders kann jeder nach seinen Vorstellungen gestalten.

An /CS schließt man das noch freie Speicherauswahlsignal (Adresse

1C00H bis 1FFFH) an. /WR und /RD greift man

im schon negierten Zustand von der Grundleiterplatte hinter den

Negatoren DN21 und DN22 ab. Dann braucht keine

Negation dieser Signale auf der Zusatzplatine stattzufinden. Leider

liegen die drei bis jetzt genannten Signale

nicht am Systemsteckverbinder. Die Abgriffpunkte dieser Signale sind [2] zu entnehmen. A0 und die

Betriebsspannung

+5 V sind am Steckverbinder verfügbar.

Damit bin ich einen Kompromiß eingegangen, um den

Selektionsaufwand so gering wie möglich zu halten. Denn es wird,

innerhalb des einen KByte, nur zwischen "gerader" und "ungerader"

Speicherzelle unterschieden. Dies ist aber

völlig ausreichend. Nun wird auch klar, warum nicht alle acht

Datenausgänge des angewählten Byte zurück auf den

Bus gelegt werden dürfen. Denn dann wird der Rechner "denken" , er

hat einen freien Speicherbereich bis 1FFH

zur Verfügung, und setzt einen Stackpointer auf 2000H. Dieser

müßte dann nach jedem Einschalten mittels des

R-Befehls auf 1C00H zurückgesetzt werden.

Wird mit gesteckter IS-Prüfplatine ein anderes Programm

geschrieben, könnte es zu Fehlfunktionen kommen, wenn

der Stackpointer auf 2000H steht.

An die Punkte "1" bis "14" wird die zu testende IS parallel auf die

internen Datenleitungen der Speicherzelle

aufgeschaltet. Der Schaltkreis bildet nun, je nach seiner logischen

Funktion, das gespeicherte Datenwort nach.

Die so geänderten Daten werden dann vom Rechner entsprechend

ausgewertet. Die Widerstände R1 bis R16 begrenzen

die dabei auftretenden Kurzschlußströme. R12 und R13 sind

für eine Erweiterung gedacht, um eventuell auch

18polige IS zu testen.

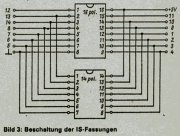

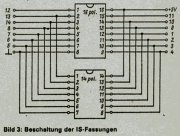

Bild 3 zeigt die Beschaltung

der beiden IS-Fassungen. Die Anschlüsse der Fassungen sind durch

Brücken miteinander

zu verbinden. Diese Brücken sind im Bild 5

aus Gründen der

Übersichtlichkeit nicht eingezeichnet. Zwei

Fassungen sind notwendig, damit die Betriebsspannungen zwischen 14- und

16poligen IS nicht umgeschaltet werden

müssen. Die Schaltung hat eine Stromaufnahme von 140 mA.

Das Programm habe ich in den in [3] beschriebenen Rahmen

"gepackt". Es wird mit dem Kennbuchstaben "K" gestartet.

Er läßt sich auf der Adresse 4882H ändern. Zur Ausgabe

der Überschrift und der Typenbezeichnung der geprüften

IS benutzt man den in [3]

erwähnten Unterprogrammaufruf.

Wer über eine Speichererweiterung verfügt, kann das Programm

auch dort an beliebiger Stelle ablegen.

Es ist relocatibel. Nicht zu belegen ist der Adreßbereich 1C00H

bis 1FFFH, da hier die Arbeitszellen des

Programms liegen. Befindet sich auf diesen Adressen ein

Arbeitsspeicher, ist er anders zu selektieren oder

vorübergehend abzuschalten (/CS auf +5 V). Besser ist es aber, die

Arbeitszellen zu verlegen. Dazu werden

im Programm auf 4892H und 4895H die Adressen entsprechend

geändert. Dann bleibt die Kompatibilität des Rechners

erhalten. Nach dem Start erscheint in der nächsten Zeile die

Zeichenkette "IS-TEST". Dahinter, getrennt durch

drei Leerzeichen, die Typenbezeichnung der gefundenen IS. Befindet sich

keine, eine unbekannte oder eine bekannte,

aber defekte IS in einer der beiden Fassungen, erscheint die

Zeichenfolge "NEGATIV". Dann meldet sich der

Monitor mit dem Promptsymbol. Nun kann das Programm erneut gestartet

oder eine andere Routine aufgerufen werden.

Im ersten Prüfschritt legt das Programm an alle IS-Pins

(Betriebsspannungsanschlüsse ausgenommem) H-Pegel.

Nun erscheinen an allen NAND-Gatterausgängen L-Pegel. Das so

entstandene Datenwort wird vom Computer ausgewertet.

Damit hat der Rechner die IS schon identifiziert. Anschließend

überprüft er nur noch die logischen Funktionen.

Dazu werden immer die falschen Pegel an die Gatterausgänge gelegt.

Ist das zu prüfende Gatter in Ordnung,

überschreibt es den falschen Pegel mit seiner "Antwort". Deshalb

sind die Widerstände R1 bis R16 notwendig.

Aber nur dadurch ist es möglich, auch IS mit

Open-Kollektor-Stufen, z.B. D 147 D, zu testen. Noch deutlicher

wird es bei den IS-Typen D 100 D und D 103 D, da sie ja die gleichen

logischen Funktionen haben. Mit einer

PIO könnte hier kein Unterschied festgestellt werden.

Das Programm unterscheidet zwischen den IS D 100, D 103, D 104, D 108,

D 110, D 120, D 130, D 147, D 192, D 193

und D 195. Funktionsgleiche IS lassen sich natürlich nicht

unterscheiden, (z.B. D 204 und P 104 oder D 140 und D 120).

Pinkompatible Low-Power-Schottky-Schaltkreise zu testen, ist

uneingeschränkt möglich. Vor dem Testen von

CMOS-IS wird gewarnt. Die Kurzschlußströme würden sie

zerstören.

Die Schaltung läuft auch mit Schaltkreisen der

P-Serie störungsfrei.

Wird die Leiterplatte nur mit den IS D1 bis D4 und D13, D14

bestückt, ergibt sich ein 16 Bit breites Ausgabeport.

Es kann mit dem BASIC-Befehl POKE programmiert und für Steuerungen

genutzt werden.

Denkbar wäre eine Erweiterung des Programms auf alle 14- und

16poligen TTL-IS. Eine Grafik mit dem

Anschlußbelegungsplan der gefundenen IS könnte die

Anschaulichkeit erhöhen.

| [1] | Heyder, F.: Amateurcomputer "AC1", FUNKAMATEUR 32, 33, 34, (1983 bis 1985), Beitragsfolge 1 bis 12 |

| [2] | Heyder, F.: Amateurcomputer "AC1", Teil 8 FUNKAMATEUR 33 (1984), H.9, S.443 |

| [3] | Heyder, F.: Amateurcomputer "AC1", Teil 10 FUNKAMATEUR 33 (1984), H.11, S.562 |

| [4] | Claßen, Oefler: Wissensspeicher

Mikrorechnerprogrammierung, VEB Verlag Technik, Berlin 1986 |

| [5] | Aktive elektronische Bauelemente 1984/85 VEB Kombinat Mikroelektronik, Erfurt, Teil 1 |

|

|

|

| 170 KByte | 55 KByte | 60 KByte |

| Bild 1 | Bild 2 | Bild 3 |

| Speicher | Steuersignale | IS-Fassungen |

|

|

|

| 238 KByte | 218 KByte | 280 KByte |

| Bild 4 | Bild 5 | Bild 6 |

| Leiterseite | Bestückungsplan | Hex-Listing |